约 604 个字 3 行代码 2 张图片 预计阅读时间 3 分钟 共被读过 次

lec13-RISC-V的控制器实现与流水线入门

单周期数据路径

核心组件

- 5个阶段:IF(取指)、ID(译码)、EX(执行)、MEM(访存)、WB(写回)

- 关键单元:

IMEM(指令存储器)RegFile(寄存器文件)ALU(算术逻辑单元)DMEM(数据存储器)Imm Gen(立即数生成器)Branch Comp(分支比较器)

数据路径示例

VerilogPC → IMEM → RegFile → ALU → DMEM → RegFile

↑ ↑ ↑

Imm Gen Branch Comp WB Mux

控制逻辑设计

控制信号真值表(部分)

| 指令 | PCSel | ImmSel | ALUSel | MemRW | RegWEn | WBSel |

add | +4 | - | Add | Read | 1 | ALU |

lw | +4 | I | Add | Read | 1 | Mem |

sw | +4 | S | Add | Write | 0 | - |

jal | ALU | J | Add | Read | 1 | PC+4 |

beq | ALU | B | Add | Read | 0 | - |

- 字段说明:

ImmSel:立即数类型(I/S/B/J/U)WBSel:写回数据来源(ALU/Mem/PC+4)*表示无关项,-表示无操作

控制器实现方案

- ROM:查表式控制,适合手动设计

- 组合逻辑:通过逻辑门实现,可优化共享子表达式

指令时序与性能衡量

典型指令时序(单周期)

| 指令 | IF (200ps) | ID (100ps) | EX (200ps) | MEM (200ps) | WB (100ps) | 总时间 |

add | ✔️ | ✔️ | ✔️ | - | ✔️ | 600ps |

lw | ✔️ | ✔️ | ✔️ | ✔️ | ✔️ | 800ps |

beq | ✔️ | ✔️ | ✔️ | - | - | 500ps |

性能公式

- 程序执行时间 =

指令数 × CPI(cycles per instruction) × 时钟周期 - 能耗公式 =

电容 × 电压² × 切换频率 - 性能权衡示例:

- 处理器A:1M指令,CPI=2.5,2.5GHz → 1ms

- 处理器B:1.5M指令,CPI=1,2GHz → 0.75ms(更快)

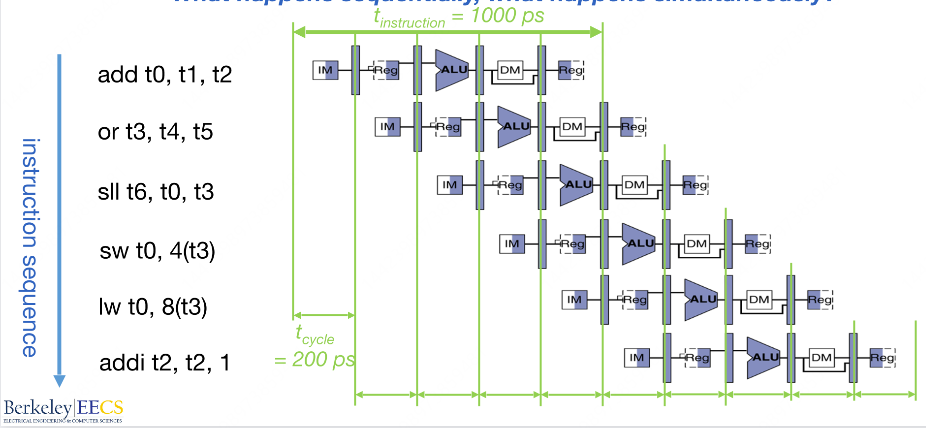

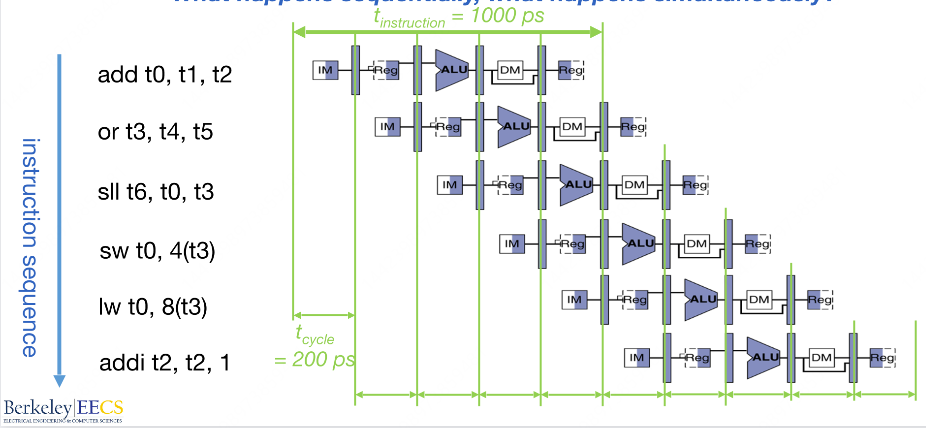

流水线设计

流水线阶段

- IF:取指令

- ID:译码 + 读寄存器

- EX:ALU计算

- MEM:数据访存

- WB:写回寄存器

流水线优势

- 吞吐量提升:各阶段并行,时钟频率提高(200ps/cycle → 5GHz)

| Single Cycle | Pipelining |

| Timing | tstep= 100 … 200 ps | tcycle= 200 ps |

| (Register access only 100 ps) | All cycles same length |

| Instruction time, tinstruction | = tcycle= 800 ps | 1000 ps |

| Clock rate, fs | 1/800 ps= 1.25 GHz | 1/200 ps= 5 GHz |

| Relative speed | 1 x | 4 x |

流水线数据路径

关键挑战

- 冒险处理:结构冒险(资源冲突)、数据冒险(依赖)、控制冒险(分支预测)

- 控制信号传递:需将控制信号沿流水线寄存器传递至对应阶段

总结:RISC-V单周期设计通过统一数据路径支持所有指令,但性能受限于最长路径。流水线通过阶段并行提升吞吐量,但需解决冒险问题。控制逻辑通过真值表驱动,支持灵活扩展。性能需综合考虑指令数、CPI和时钟频率。